Hội thảo chủ đề "Optimisation des performances d'applications avec mémoire transactionnelle"

Thứ ba - 18/12/2012 10:20Thứ Năm ngày 20/12/2012 tại IFI sẽ diễn ra buổi hội thảo với chủ đề "Optimisation des performances d'applications avec mémoire transactionnelle: Une approche par apprentissage automatique » do giáo sư Jean-Francois...

Thứ Năm ngày 20/12/2012 tại IFI sẽ diễn ra buổi hội thảo với chủ đề "Optimisation des performances d'applications avec mémoire transactionnelle: Une approche par apprentissage automatique » do giáo sư Jean-Francois Méhaut (UJF-CEA/LIG) trình bày

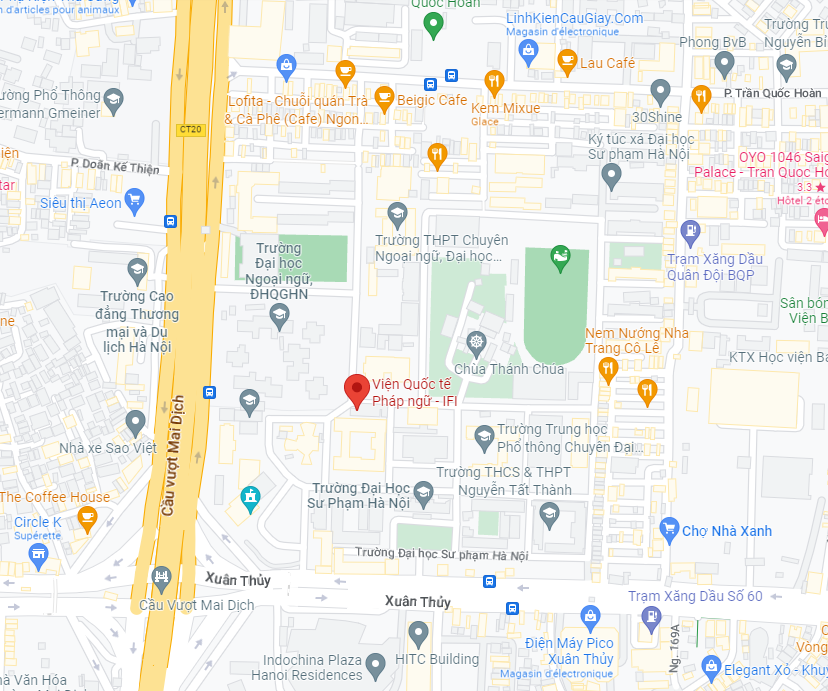

+ Thời gian : vào 16h ngày 20/12

+ Địa điểm : Hội trường

+ Diễn giả : Giáo sư Jean-Francois Méhaut

Tóm tắt

Tác giả: Bastos Castro (INRIA/LIG) và J-F. Méhaut (UJF-CEA/LIG)

Le concept de processeur multicoeurs constitue le facteur dominant pour offrir des hautes performances aux applications parallèles. Afin de développer des applications parallèles capables de tirer profit de ces plate-formes, les développeurs doivent prendre en compte plusieurs aspects, allant de l'architecture aux caractéristiques propres à l'application. Dans ce contexte, la Mémoire Transactionnelle (Transactional Memory - TM) apparaît comme une alternative intéressante à la synchronisation basée sur les verrous pour ces plates-formes. Elle permet aux programmeurs d'écrire du code parallèle encapsulé dans des transactions, offrant des garanties comme l'atomicité et l'isolement. Lors de l'exécution, les opérations sont exécutées spéculativement et les conflits sont résolus par ré-exécution des transactions en conflit. Bien que le modèle de TM ait pour but de simplifier la programmation concurrente, les meilleures performances ne pourront être obtenues que si l'exécutif est capable de s'adapter aux caractéristiques des applications et de la plate-forme.

Ces travaux concernent l'analyse et l'amélioration des performances des applications basées sur la Mémoire Transactionnelle Logicielle (Software Transactional Memory - STM) pour des plates-formes multicoeurs. Dans un premier temps, nous montrons que le modèle de TM et ses performances sont difficiles à analyser. Pour s'attaquer à ce problème, nous proposons un mécanisme de traçage générique et portable qui permet de récupérer des événements spécifiques à la TM afin de mieux analyser les performances des applications. Par exemple, les données tracées peuvent être utilisées pour détecter si l'application présente des points de contention ou si cette contention est répartie sur toute l'exécution. Notre approche peut être utilisée sur différentes applications et systèmes STM sans modifier leurs codes sources.

Ensuite, nous abordons l'amélioration des performances des applications sur des plates-formes multicoeurs. Nous soulignons que le placement des threads (thread mapping) est très important et peut améliorer considérablement les performances globales obtenues. Pour faire face à la grande diversité des applications, des systèmes STM et des plates-formes, nous proposons une approche basée sur l'Apprentissage Automatique (Machine Learning) pour prédire automatiquement les stratégies de placement de threads appropriées pour les applications de TM. Au cours d'une phase d'apprentissage préliminaire, nous construisons les profiles des applications s'exécutant sur différents systèmes STM pour obtenir un prédicteur. Nous utilisons ensuite ce prédicteur pour placer les threads de façon statique ou dynamique dans un système STM récent.

Dans la dernière partie de l'exposé, nous effectuons une évaluation expérimentale et nous montrons que l'approche statique est suffisamment précise et améliore les performances d'un ensemble d'applications d'un maximum de 18%. En ce qui concerne l'approche dynamique, nous montrons que l'on peut détecter des changements de phase d'exécution des applications composées des diverses charges de travail, en prévoyant une stratégie de placement appropriée pour chaque phase. Sur ces applications, nous avons obtenu des améliorations de performances d'un maximum de 31% par rapport à la meilleure stratégie statique.

Tham khảo:

M. Castro, L. F. W. Góes, L.G. Fernandes and J.-F. Méhaut.

"Dynamic Thread Mapping Based on Machine Learning for Transactional Memory Applications" In International European Conference on Parallel

and Distributed Computing (Euro-Par), August 2012

M. Castro, L. F. W. Góes, C. P. Ribeiro, M. Cole, M. Cintra and J.-F. Méhaut, "A Machine Learning-Based Approach for Thread Mapping on Transactional Memory Applications", International Conference on High Performance Computing (HiPC), December 2011

M. Castro, K. Georgiev, V. Marangonzova-Martin, J.-F. Méhaut, L. G. Fernandes and M. Santana, "Analysis and Tracing of Applications Based on Software Transactional Memory on Multicore Architectures" In

Euromicro International Conference on Parallel, Distributed and Network-Based Computing (PDP), February 2011.

Nhiệt liệt chào đón các bạn!

Những tin mới hơn

Những tin cũ hơn